Si5351をVFOにする

TA7358 CWの回路VFOにAD9833を使ってきた。難点は発振周波数が高くできないので受信・送信周波数より低い周波数で出力することになる。するとスプリアスの抑制が困難になってきた。それに送信周波数を直接出力できないので送信にも周波数変換が必要になるため回路規模が大きくなってしまう。

送信系統比較

AD9833

Si5351

Si5351VFO[+5.5dbm]-励起(2SC1815)-電力増幅(TTC015B)-LPF-ANT

というわけで、Si5351を使ってみることにしたわけだが・・・・どこのページをみても、どうしても面倒な設定が必要なことがわかる。DDSのように簡単にはいかないようである。

自作・実験・Audio・Linux覚書: Si5351を使った7MHz VFOの実験

では、JA2GQPさんのスケッチを使わせてもらった。今回もそれを改変してCLK0で受信VFOを、CLK1で直接送信周波数を出力できるようにしたい。

回路図

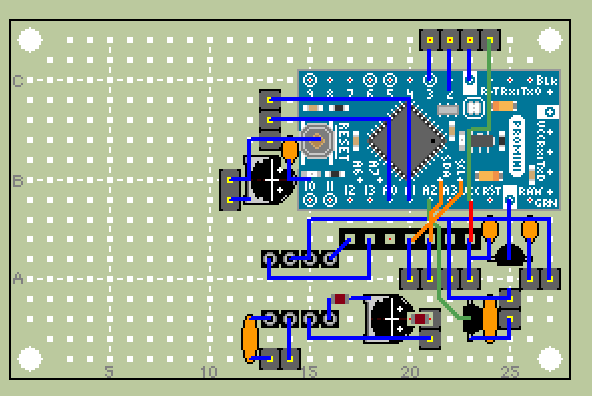

PasSによる配線図

さて、Si5351のスケッチだが、arduinoには面倒な設定がいらないライブラリがある。これを使うと簡単にスプリアスの少ない組み合わせを自動的に設定してくれるようだ。

すばらしい。。

それに、JA2GQPさんのスケッチが非常によくできていて読みやすいので助かった。受信用にCLK0を使い17MHzを出力させTX時にCLK1に7MHzを出力させるように改変した。

めずらしく、一発で思い通りに動かせた。自分用にスケッチファイルを貼っておくことにする。

https://drive.google.com/file/d/1Em5VaG_Ot9FjmdgrPUIFk0gaj6fmQSRU/view?usp=sharing

スケッチ改変点

- 送信時と受信時に異なるLowPassフィルタを使うためにCLK1を増設した。CLK1は送信用VFO出力としTXがスイッチされた時だけ出力。CLK0は受信用VFO専用とした。(こちらはTXスイッチ時も出力)

- Sメータの振れがよくない(AGC整流電圧が3.3Vまでいかない)のでAnalogRead値を、×4とし1023を超えるものを1023に制限した。

- 周波数stepをエンコーダのプッシュスイッチで制御するので長押しで順方向、短押しで逆方向にstepするようにした。stepは50,500(Hz),5k(Hz)とした。

※フォントの変更が必要だが未実装なので表示はオリジナルの50,100,1kのまま。実装方法が理解できたら変更する。

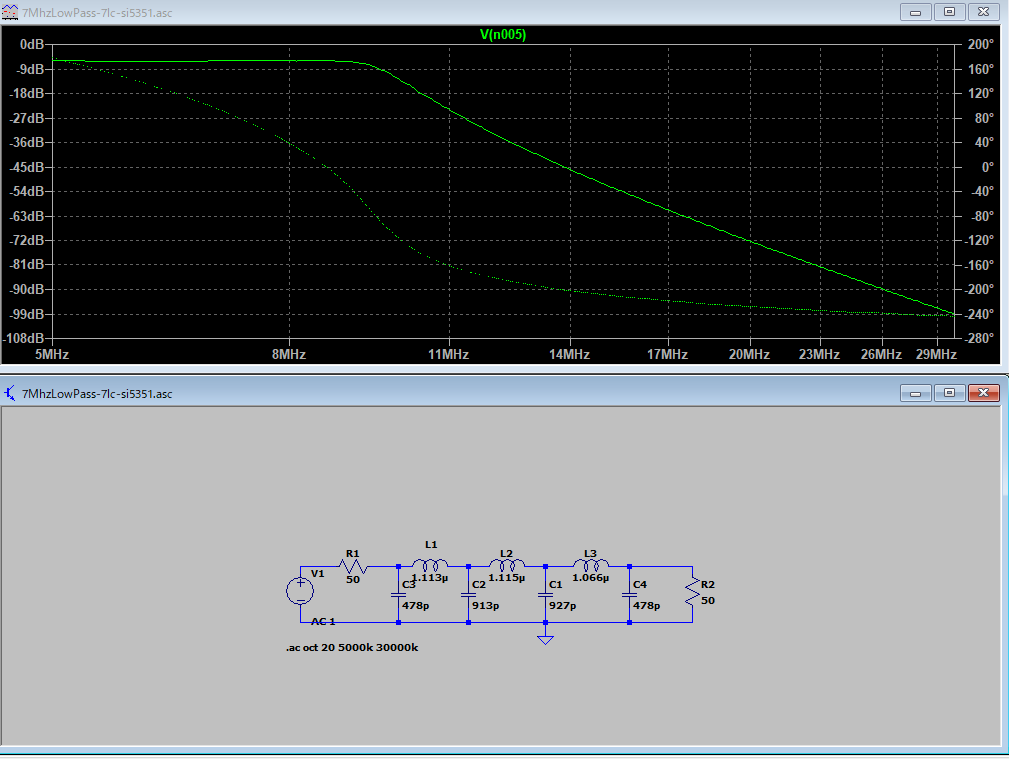

LowPassフィルタ

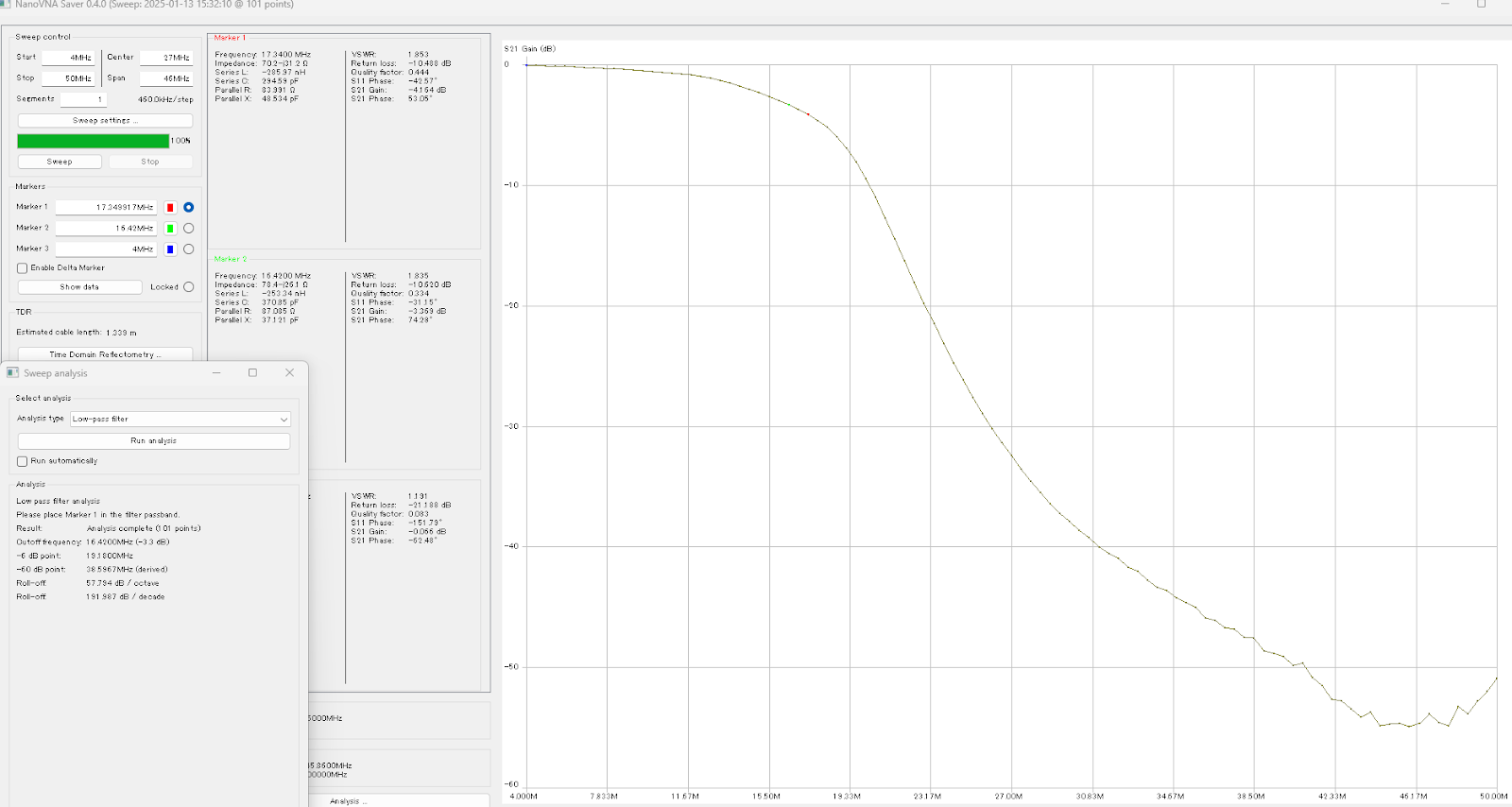

CLK0受信用

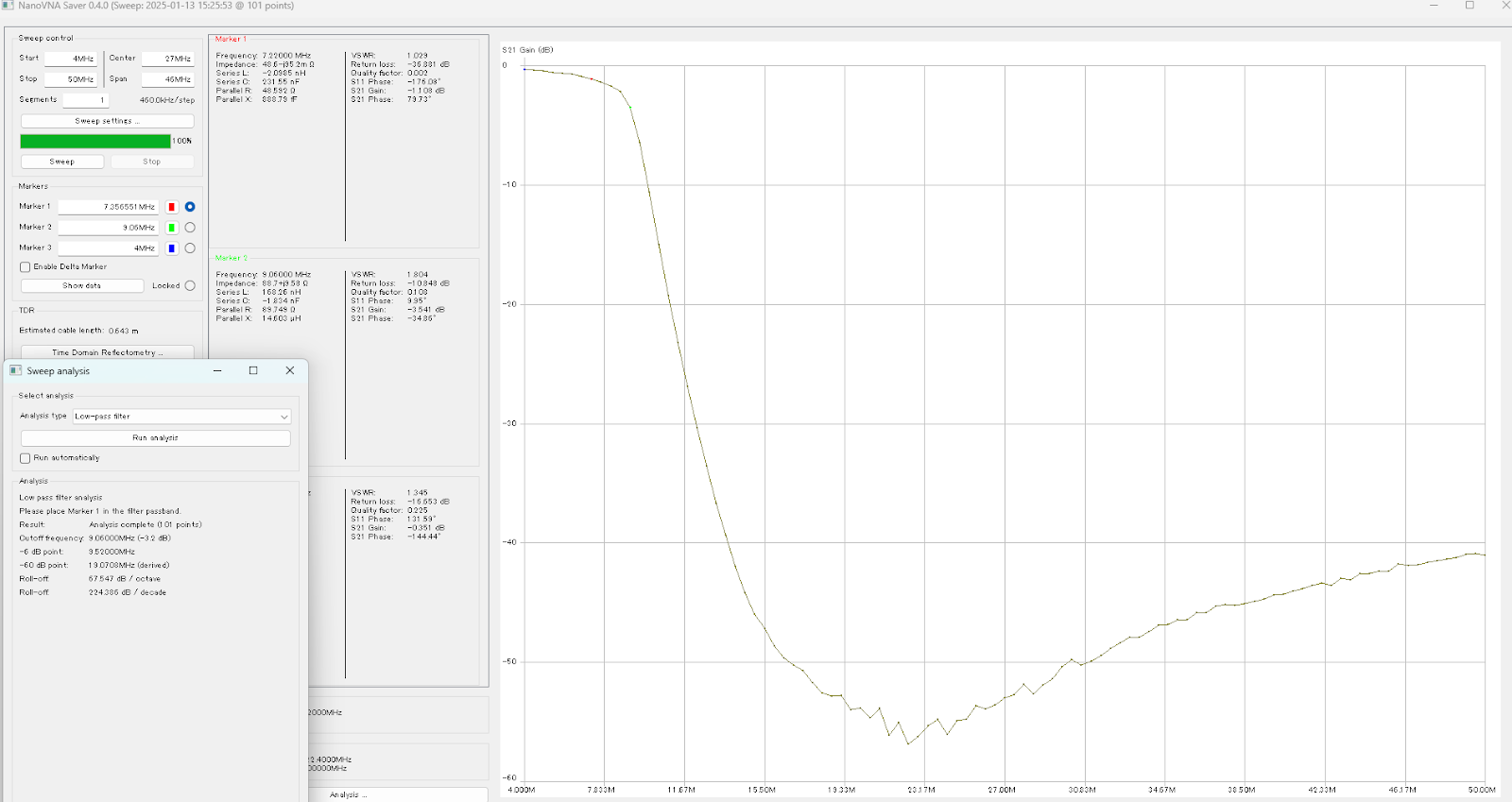

設計値では22MHzあたりから下がるようにするつもりだったが・・・CLK1送信用

CLK1出力をTinySAでみてみた

おおむねいい感じに出力されている。出力も5.5dbmあり、この後2段の増幅で使えそうな感触を得た。また、送信時にも受信用CLK0は出力されたままなのだが、受信音に変化はなく、送信周波数の飛び込み等の干渉はないようだ。

0 件のコメント:

コメントを投稿